千兆以太网UDP协议Verilog代码FPGA实现,支持UDP协议,包含ARP、ICMP、UDP功能,支持ping命令,方便实际应用。UDP协议纯Verilog代码实现,IP仅使用了Xilinx内部的FIFO/RAM,方便不同平台适配。

在FPGA上使用Verilog实现千兆以太网的UDP协议具有多项显著优势,尤其适用于对性能、实时性和资源效率要求较高的应用场景,以下是主要优势:

1. 高吞吐量与低延迟

FPGA硬件并行处理能力使得UDP数据包可以接近理论带宽。相比于软件协议栈(如Linux内核中的UDP/IP),FPGA实现避免了操作系统调度、中断处理和内存拷贝等开销,端到端延迟可降至微秒级甚至纳秒级。

2. 确定性与实时性

FPGA逻辑是硬连线的,行为可预测,适合硬实时系统(如工业控制、雷达信号处理、高频交易等),不受操作系统任务调度、垃圾回收或上下文切换影响。

3. 资源高效与定制化

支持自定义数据格式,直接对接用户逻辑(如ADC/DAC、图像传感器、高速串行接口等),减少中间缓冲。

5. 与物理层(PHY)紧密集成

FPGA通常支持RGMII/GMII/MII等以太网MAC接口,可直接连接千兆PHY芯片。可实现MAC层完全自主控制,包括帧间隔、CRC生成、流量控制等。

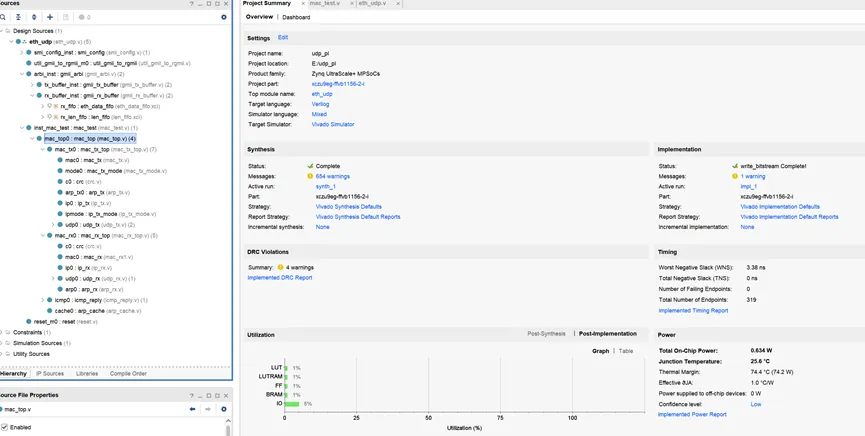

工程代码适配到Zynq UltraScale+ MPSoCs

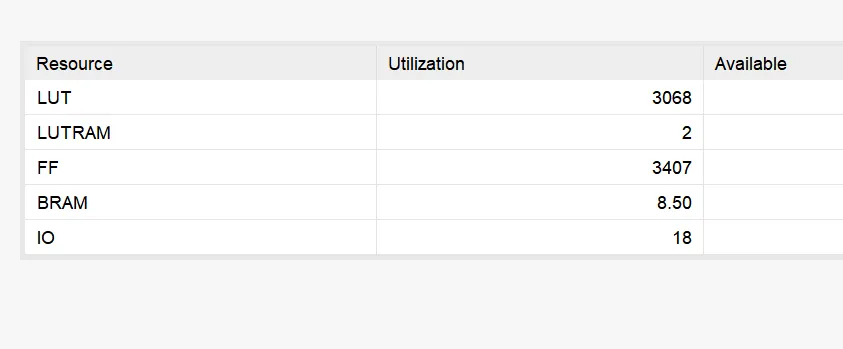

资源使用情况:

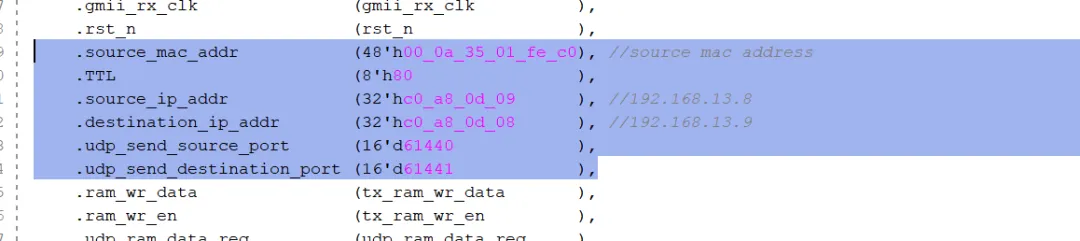

IP地址,端口号,物理地址设置

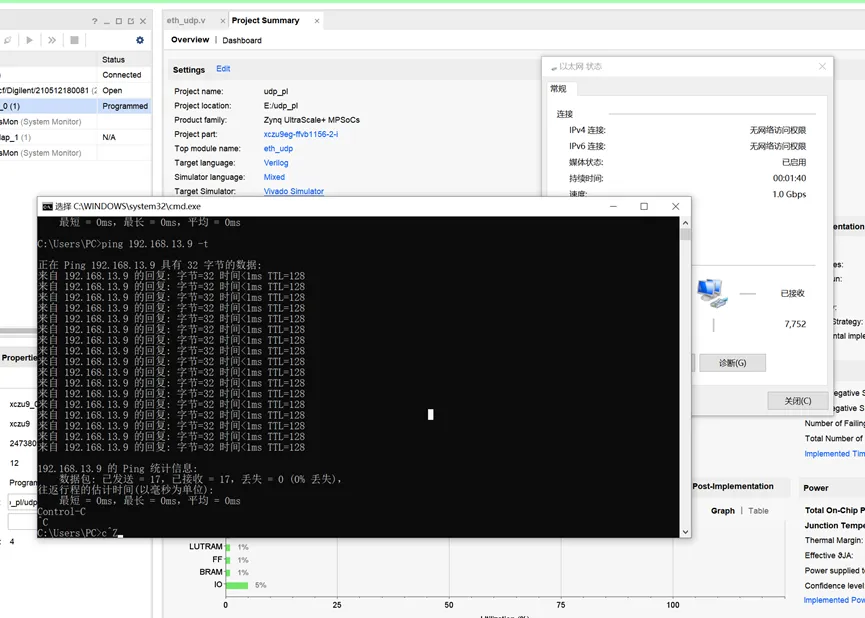

ping命令测试

需要工程源码请私信。