可编程PIC+硅光+钛酸钡异质集成---高速非易失性钛酸钡现场可光子门阵列(CeaLTILumiphaseiPronics)46寸全国产钛酸钡薄膜晶圆

- 2026-03-24 00:55:25

摘要

可编程集成光子学旨在复制光学领域中场可编程门阵列的多功能性。然而,由于传统挥发性相位移器的高功耗和热串扰,扩大这些系统的规模一直受到限制。在此,我们展示了第一个非挥发性的场可编程光子门阵列,该阵列在混合硅-钛酸钡平台上实现。与传统的热光学器件需要持续电力来维持状态不同,我们的设备利用铁电域切换提供非挥发性存储,使光电路能够在无需保持电力或电偏置的情况下进行编程并保持状态。六边形波导网格集成了58个可编程单元和116个执行器,实现了80纳秒的纳秒级开关速度,同时将静态功耗降低到微不足道的水平(每π相位移仅560纳瓦)。为了验证这一平台,我们将网格配置为执行多种信号处理功能,包括可调滤波、4×4线性单位变换和光路由。本研究确立了非挥发性铁电硅光子学作为一种可扩展、无热的平台,为下一代能源高效光子计算奠定了基础。

关键词:可编程集成光子学,非挥发性,钛酸钡,铁电域切换,能源高效光子学。

#0:10mm-10mmsto衬底-bto薄膜(300nm厚度可定制)

#1:sto外延片

2寸 外延 sto 2-20nm(可定制)- 2um Sio2(可定制) -Si(可定制)

#2:a向 bto外延片

2寸 外延 a-向 bto(300nm或者500nm,或者定制)-sto 8nm(可定制)- 2um Sio2(可定制) -Si(可定制)

#3:C向 bto外延片

2寸 外延 c-向 bto(150nm或者300nm,或者定制)-sto 8nm(可定制)- 2um Sio2(可定制) -Si(可定制)

#6寸DUV步进式光刻代工,最小线宽180nm,超高性价比,可以只曝光

#提供8寸 8umSiO2热氧片,6寸15um热氧片 10um 8um热氧片 8寸10um热氧片

ALOOI晶圆;--氧化铝薄膜晶圆,键合工艺和镀膜工艺

TAOOI晶圆--氧化钽薄膜晶圆,镀膜工艺

SINOI晶圆--超低损耗氮化硅薄膜晶圆,210nm-300nm-400nm-800nm

SICOI晶圆;新型量子光学平台500nm-700nm-1um

6寸LTOI晶圆批量供应;铌酸锂的有力的竞争对手,薄膜钽酸锂晶300600

8寸LNOI晶圆;8寸LNOI助力更大规模薄膜铌酸锂产品量产

LN/LT-SOI/Si/SIN W2W&D2W异质集成

流片: 6寸 氮化硅 铌酸锂 硅光 超高性价比流片, 1个BLOCK的价格买一整片晶圆

划重点--全国产-超高性价比-6 寸硅光-氮化硅-铌酸锂流片白皮书

我们为客户提供晶圆(硅晶圆,玻璃晶圆,SOI晶圆,GaAs,蓝宝石,碳化硅(导电,非绝缘),Ga2O3,金刚石,GaN(外延片/衬底)),镀膜(PVD,cvd,Ald,PLD)和材料(Au Cu Ag Pt Al Cr Ti Ni Sio2 Tio2 Ti3O5,Ta2O5,ZrO2,TiN,ALN,ZnO,HfO2。。更多材料),键合(石英石英键合,蓝宝石蓝宝石键合)光刻,高精度掩模版,外延,掺杂,电子束光刻等产品及加工服务(请找小编领取我们晶圆标品库存列表,为您的科学实验加速。

请联系小编免费获取原文

1. 引言

可编程集成光子学(PIP)承诺将可重构电子学的多功能性引入光子电路,2从而为包括6G通信、数据中心互联、物联网(IoT)、高科技医学、人工智能、光子处理、神经形态计算和量子计算等众多应用提供灵活、低功耗且具成本效益的平台。为了应对这些应用领域日益增长的需求,未来几年将需要扩展可编程光子电路,集成超过10⁴个执行器,这将需要同时解决几个目前尚未被当前硅光子学热光学(TO)和微电机电系统(MEMS)相位移技术克服的挑战。26-29 从本质上讲,要求实现具有最小占地面积(小于100 µm)、低损耗(小于0.15 dB)、低功耗(小于1 mW/π),并且具有纳秒级调节速度的可编程单元(PUC),以实现复杂的多端口干涉仪和波导网格。基于TO的相位移器会消耗适度的静态功率(1-10 mW/π),而基于机械效应的相位移器在设备处于待机状态时需要持续偏置电压。因此,静态能耗很容易随着执行器数量的增加而扩大,从而导致可编程处理器的功率预算显著增加。

非挥发性材料,如相变化合物、铁电材料和忆阻氧化物,已被提出作为集成相位移器的替代方案,因为它们的光学状态可以在没有任何功耗或偏置的情况下保持。在不同的选择中,相变材料(PCM)、铁电材料和忆阻氧化物在过去几年中作为替代方案得到了研究,它们提供了可逆开关功能,具有超低功耗和潜在的快速响应。30尽管这些材料平台各自展示了有希望的进展,但它们的局限性已将实验演示限制在仅仅适用于小规模电路,远远低于实现完全可编程通用光子处理器所需的规模。

相变材料(PCMs),如Ge2Sb2Se5(GST),是可以通过电场在有序晶态和无序非晶态之间开关的硫属化合物,提供相位变化。相变材料在硅波导中的集成已有报道,其中通过热光效应实现相位变化31-33,该技术展示了潜在的快速开关速度(0.1 µs,1 mW)用于设定非晶化相,并且具有潜在的低占地面积(Lπ=10-50 µm)。然而,转化为晶化相的开关速度是毫秒级的,导致功耗达到十几毫瓦。另一个缺点是,由于相变材料与硅波导中的光学模式过于接近,导致损耗较大(>0.33 dB)。这些限制阻碍了基于该技术的光子处理器的可扩展性。

忆阻器通常由导体-绝缘体-导体三层组成34。导体层可以由金属或半导体制成,而绝缘体则是介电材料。施加足够的电压会形成导电丝,从而将忆阻器从初始的高阻态(HRS)切换到低阻态(LRS)。通过反转偏置极性可以将忆阻器恢复到高阻态,从而断开导电丝。随后,结合自由载流子弥散效应来实现可控的相位变化。最近的实验35报告了一种基于异质集成GaAs/Al2O3/Si忆阻器的硅光子相位移器,集成在一个10 µm的微环谐振器中,具有低插入损耗(<0.05 dB)。尽管在开关速度(<1 ns)、开关功率(150-360 µW)和插入损耗(0.27 dB)方面的结果令人鼓舞,但相位移器的紧凑性受到Lπ(350 µm)较大值的限制。

铁电材料,特别是钛酸钡(BTO),近年来作为高效相位移器的有前景材料得到了关注。BTO具有报告中最高的泊克尔斯系数之一(r42约为923 pm V−1),并且其与硅光子电路的大规模集成潜力已通过外延生长和直接晶圆粘接的组合得到了证明36。BTO还允许通过施加电场切换非挥发性铁电域来存储光学信息。首次演示确实实现了8级的多级存储37,尽管在该平台上开发的初始设备显示出较大的Lπ(1mm)和适中的开关速度(约微秒)用于非挥发性操作。该平台显然具有改进潜力,以实现紧凑的占地面积、超低插入损耗、亚毫瓦级开关、纳秒级重构和非挥发性。

在此,我们介绍了基于钛酸钡(BaTiO₃)执行器的第一个非挥发性场可编程光子门阵列(FPPGA)。 该FPPGA在一个扁平化的六边形波导网格配置中集成了116个执行器或相位移器,并实现了纳秒级开关,单个执行器的功耗低于微瓦,比现有技术低两个数量级。我们实验演示了多个关键的信号处理应用,包括可重构滤波器、单位线性变换、光路由和光分裂。此外,我们展示了个别可编程单元(PUC)能够在外部偏置关闭后设置并保持特定状态的能力,这得益于它们的非挥发性行为。这些特性标志着向大规模、低功耗的可编程光子系统迈出了重要的一步。

2. 结果

可编程光子集成电路使用相互连接的波导网格,其中可重构的2×2元件,称为PUC或门,定义并控制传播通过网络的光信号的幅度和相位。遵循电子场可编程门阵列(FPGA)的理念,光子FPGA(FPPGA)可以通过配置其PUC并选择合适的端口来重新编程,实现各种光子电路和线性多端口变换。38,39常见的PUC实现基于一个平衡的Mach-Zehnder干涉仪(MZI),该干涉仪由两个50:50多模干涉器(MMI)和每个臂上的电偏置相位移器组成。使用具有非挥发性执行器(NV-PUC)的PUC作为基本构建块可以消除静态功耗,因为每个状态可以设置一次,并且无需持续偏置即可保持。

图1. 非挥发性FPPGA的设计原理与物理实现a. 基于六边形波导网格拓扑的可编程光子芯片的艺术渲染图。b. 混合硅-钛酸钡平台上的非挥发性相位移机制示意图。电压脉冲重新定向铁电域(蓝色),改变有效折射率而不消耗静态功率。c. 装配并通过引线焊接的芯片的照片,安装在印刷电路板(PCB)上。d. 显微镜下的光学图像,显示单个NV-PUC的细节。e. 放大后的显微镜图像,显示制造的六边形网格,展示了单元格的大规模集成和互联的BTO执行器。

图1展示了非挥发性FPPGA的设计原理和物理实现。图1a中的示意图描绘了基于六边形波导网格拓扑的FPPGA,使得可以进行软件定义的光子电路编程。图1b详细介绍了这种可重构性的基本机制,其源于在混合硅-钛酸钡(Si-BTO)平台上实现PUC。通过施加电压脉冲,BTO层中的铁电域被重新定向,从而改变有效折射率并提供非挥发性相位移。该设计的实现如图1c所示,展示了在印刷电路板上的已制造和接线芯片。光学显微镜图像进一步提供了设备的细节:图1d展示了单个可编程单元的特写,而图1e展示了这些单元在六边形网格中的大规模集成,采用扁平化设计。制造电路的占地面积为2×10 mm²,包含58个PUC、116个BTO相位移器和34个光学输入/输出端口。

2.1 非挥发性可编程单元

NV-PUC作为网格电路的基本可重构元件。相位移器通过与硅波导集成的铁电BTO实现,按照方法部分描述的制造过程进行。单元的编程依赖于电控BTO执行器,通过施加横向电场来实现。通过调整干涉仪臂之间的差分相位,NV-PUC可以在其直线和交叉状态之间切换,或提供模拟耦合调节。

BTO执行器的集成使得NV-PUC可以根据施加电压的特性,在挥发模式和非挥发模式下操作。当NV-PUC在挥发模式下运行时,直流电压通过泊克尔斯效应改变BTO的折射率。在非挥发模式下,其铁电域配置发生变化,从而实现非挥发性相位移。在该过程中,外部电场的应用会引起铁电域的重新定向,这样就能稳定地保持所需的相位状态。

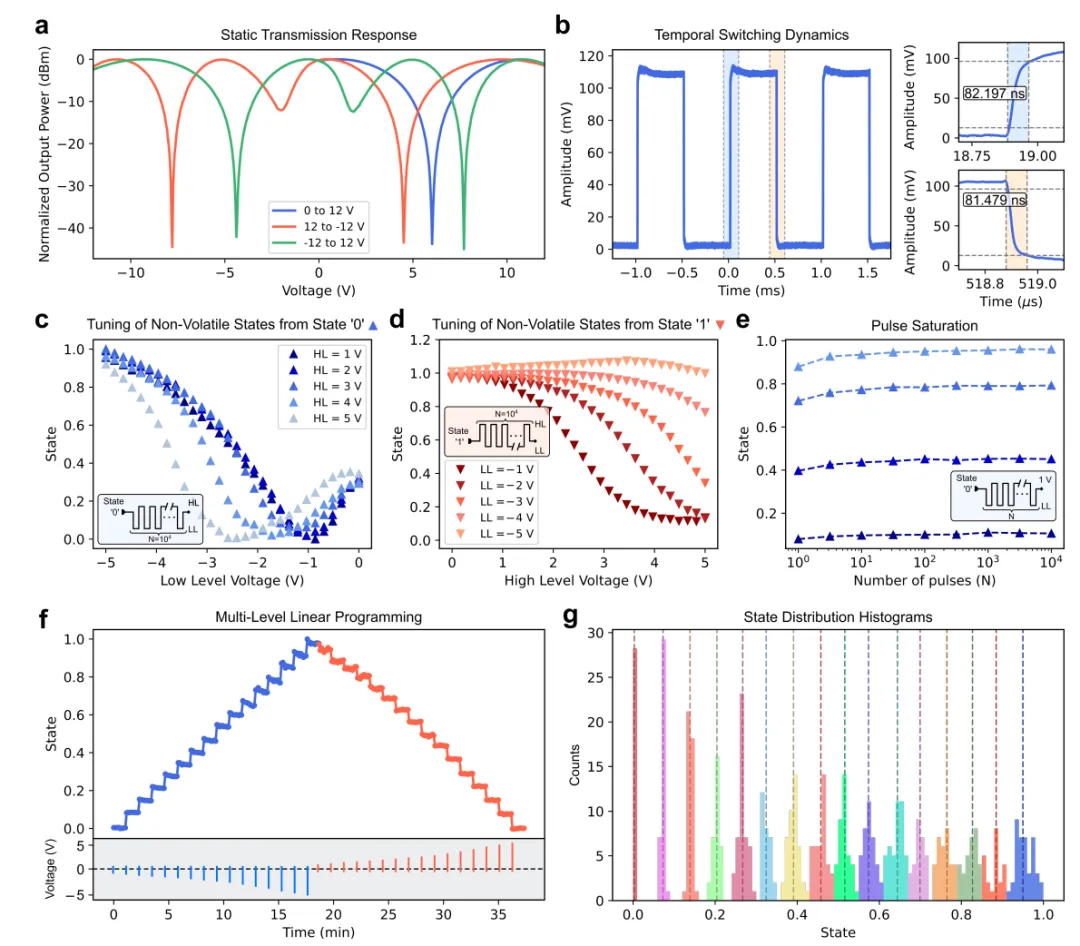

图2. NV-PUC的表征a. MZI的静态传输响应,显示了由于铁电域在直流电压扫描下重新定向而产生的典型蝴蝶形滞回回路。b. 时间开关动态,演示了约82纳秒的对称上升和下降时间,由泊克尔斯效应驱动。c, d. 通过施加具有不同低电平(LL)和高电平(HL)电压的脉冲序列,从状态“0”(c)和状态“1”(d)开始调节非挥发性状态。e. 状态饱和行为,作为施加脉冲数量(N)的函数,显示在超过102个脉冲后状态的稳定性。f. 多级线性编程,演示了具有16个不同相位级别的稳定“阶梯”响应。g. 从600次随机转换中获得的状态分布直方图,验证了16个可编程状态的准确性和可重复性。

图2c从状态'0'开始,表征了调谐动态。在该模式下,在施加1至5 V之间的正高电平(HL)偏置时,我们施加一个脉冲序列,将低电平(LL)电压从0扫到-5 V。图2d显示了从状态'1'开始的调谐行为。此时,设备通过将HL电压从0调节到5 V来实现调谐,反向基线的负LL电压。在此优化驱动方案下,具有350 µm活跃长度的相位移器能够实现完全的非挥发性π相位移,消光比为12 dB。

我们还研究了设备的非挥发性行为与施加脉冲数量(N)之间的关系。为此,我们应用了连续的300 ns恒幅脉冲,同时改变N。图2e显示,对于中间状态(介于0和1之间),所达到的状态在N = 102脉冲后达到饱和。这意味着为了在设备中建立一个状态,所需的脉冲序列总时间将是60 µs。

保持多个中间状态的能力使得该设备能够作为可调的构建块用于可编程光子学。为了演示这一精确控制,我们将NV-PUC初始化为状态'0',并应用了一系列特定的脉冲。这些脉冲的幅度是根据图2c–d中的数据预先计算的,以确保光学步进是线性且均匀分布的。我们编程了十六个不同的状态,每个状态保持1.2分钟,以验证其稳定性,然后再进入下一个状态。接着,使用相反极性的脉冲反转该序列。如图2f所示,设备产生了一个稳定的线性“阶梯”响应,成功地在两个方向上解析了十六个均匀分布的状态。为了确保无论先前的状态如何,都能可靠地设置任何状态,我们进行了一个随机切换测试,涉及600次转换。在该实验中,我们从十六个可用级别中随机选择目标状态。为了保证准确性,我们在每次新设置之前将设备重置为状态'0'。最终结果如图2g所示。直方图显示出十六个明显分离的峰值,证明设备能够创建一致且可重复的状态。

2.2 六边形网格可编程电路

我们首先通过对组成PUC施加直流电压扫描来进行六边形网格的静态表征,从而生成它们的光学响应曲线。表征序列是通过一个基于图形的自定义算法定义的(有关设置和表征算法的详细信息,请参见补充说明2)。得到的参数随后被存储在数据库中,允许我们精确配置后续实验中所需的特定耦合比。系统校准后,我们评估了输入和输出光栅耦合器的光谱工作范围。我们的测量表明,设备在1565 ± 15 nm的窗口内达到了峰值效率。

六边形波导网格可以配置为模拟多种光学电路的硬件架构,作为一个通用的光子处理器。该网格支持传统的前馈和反馈有限脉冲响应(FIR)和无限脉冲响应(IIR)滤波器,以及复杂的多输入/多输出(MIMO)线性光学变换器等功能。

不平衡的Mach-Zehnder干涉仪(UMZI)作为一个周期性陷波滤波器工作。这些设备是构建格滤波器和FIR横向滤波器的基本组件。通过操控PUC设置,我们成功地合成了UMZI结构,其路径长度差分别等于标准PUC长度的2倍和4倍。

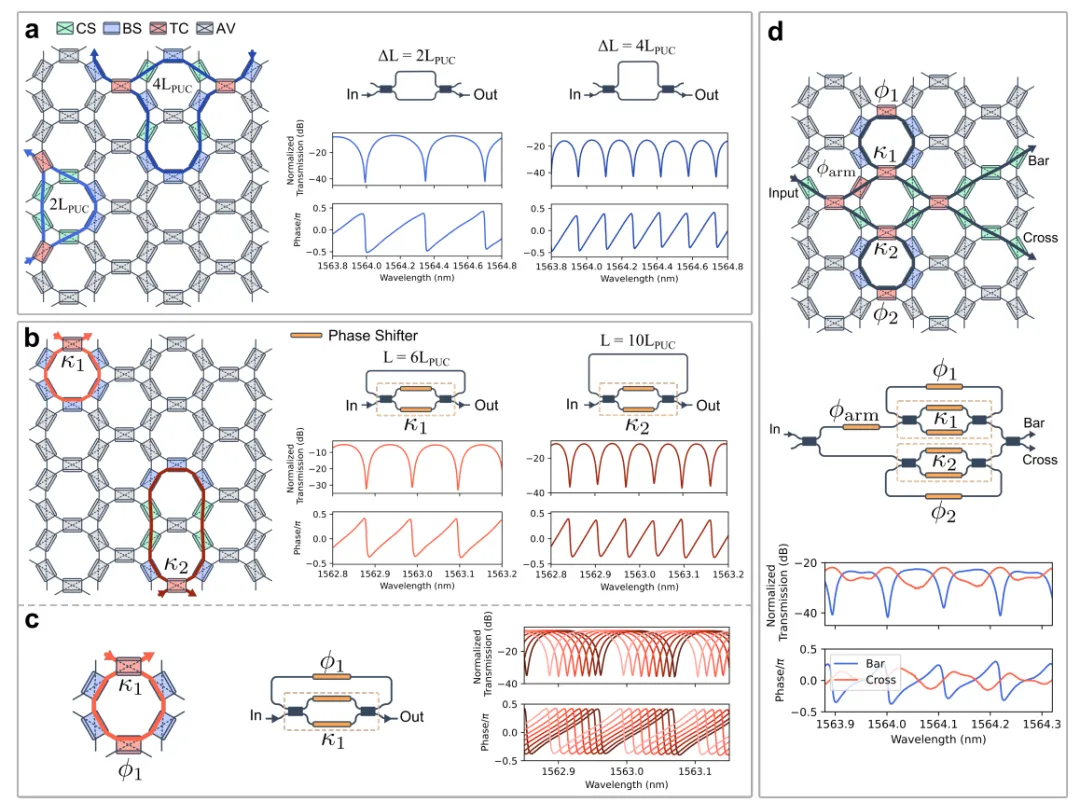

图3. 在六边形网格上实现可重构光学滤波器a. 合成的UMZI,路径长度差为 ( 2L_{PUC} ) 和 ( 4L_{PUC} ),显示了测量的归一化传输光谱和相位响应。b. 光学环谐振器,配置了腔体周长为 ( 6L_{PUC} ) 和 ( 10L_{PUC} )。c. IIR滤波器的可调性演示,通过独立控制PUC相位移器来调节共振峰。d. 一个复杂的二阶RAMZI滤波器的配置和测量的光谱响应。

图3a展示了这些配置的实验数据。这些路径不平衡导致的自由光谱范围(FSR)分别为43.65 GHz和19.02 GHz。

我们还实现了环腔,它们作为周期性滤波器工作。通过这些结构,我们可以实现全极IIR陷波滤波器,并将它们与其他结构结合,能够实现IIR陷波滤波器和混合FIR + IIR带通滤波器。这些谐振器对于组装复杂的架构至关重要,例如耦合谐振器光波导(CROW)或环辅助Mach-Zehnder干涉仪(RAMZI)。通过精确调谐单元,我们实现了具有6和10个PUC长度腔体周长的单光学环谐振器。图3b展示了这些腔体的测量数据,分别展示了13.27 GHz和7.95 GHz的自由光谱范围(FSR)值。图3c展示了IIR滤波器的可调性。通过调节PUC作为相位移器的两个执行器,我们可以独立控制耦合和输出相位。通过变化施加到两个相位移器的电压,谐振峰可以在整个光谱周期内被调节。

利用这种灵活性,我们构建了更复杂的滤波器,例如图3d所示的双环RAMZI滤波器。该结构的测量结果显示了条形和交叉输出端口,它们是互补的,且具有13.14 GHz的自由光谱范围(有关额外滤波器测量的详细信息,请参见补充说明3)。

除了滤波应用外,我们还利用六边形波导网格实现了多功能的MIMO线性光学变换。网格的可编程性使其能够模拟多种连接方案,从单位矩阵运算到复杂的路由和广播网络。

我们将六边形网格编程为实现矩形单位架构,创建了一个4×4可编程线性光学变换器。

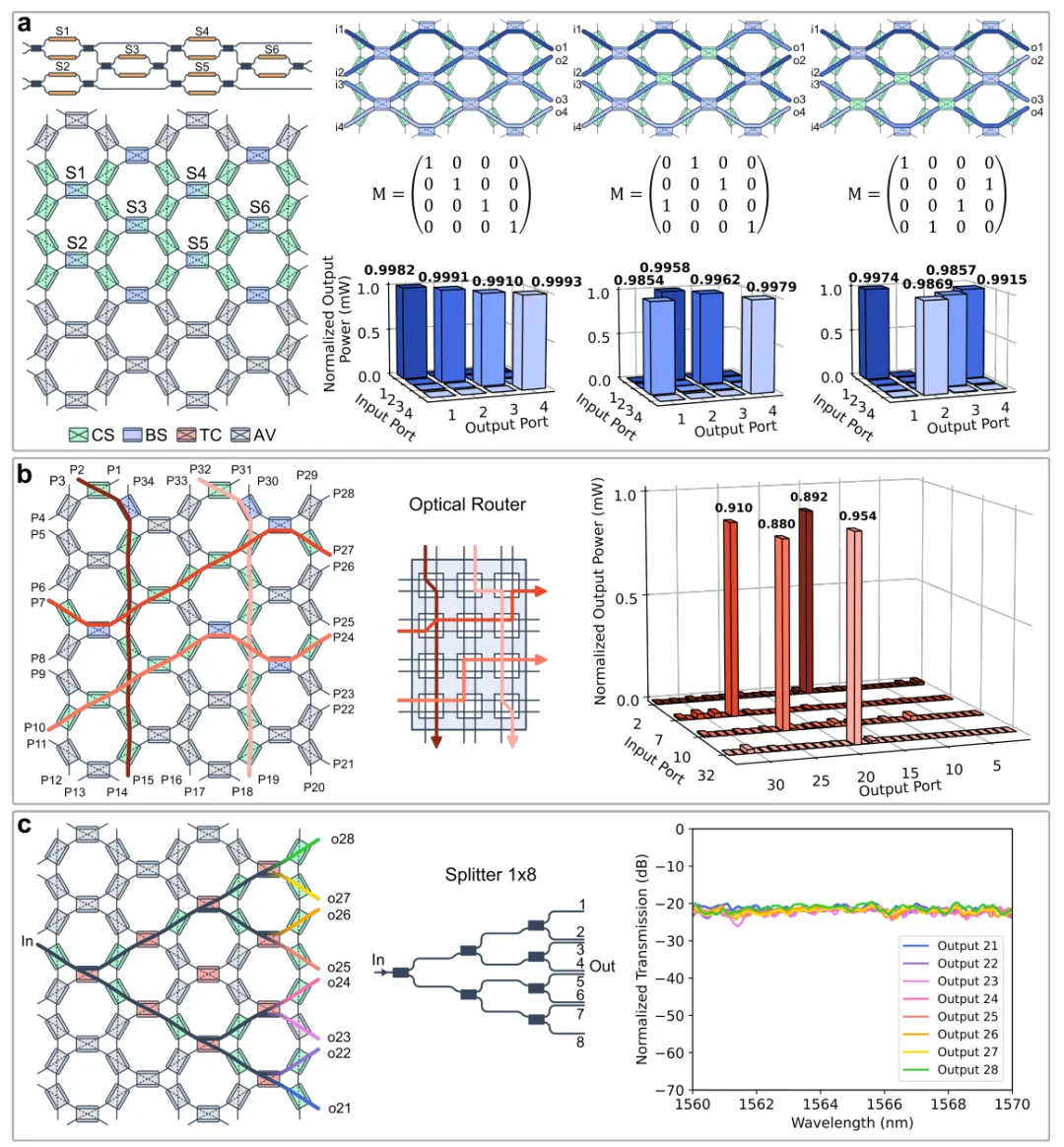

图4. 光子处理器上的线性变换与路由a. 4×4 可编程线性光学变换器。左侧:网格示意图,定义了六个活动可调耦合器(S1–S6)。右侧:目标单位传输矩阵和三种不同配置的测量归一化输出功率,展示了高保真度。b. 将网格配置为光路由器,允许四个独立信号同时路由而不发生干扰。条形图显示了每个目标端口的归一化输出功率。c. 通过级联树结构实现的1×8光分配器演示。图表显示了八个输出端口(o21–o28)的叠加传输光谱,表明功率分布均匀且具有宽带操作。

如图4a所示,通过定义六个可调耦合器(S1–S6),我们建立了一个可重构开关,能够执行多种单位运算。我们合成了三个不同的传输矩阵(M)来展示设备的切换能力。相应的条形图展示了每种配置的归一化输出功率。该设备表现出卓越的保真度,归一化输出功率始终超过0.98,并且期望连接和非期望连接之间的高传输比(~25 dB)。

为了验证平台的互连能力,我们将网格编程为一个灵活的光路由器。图4b展示了一个多路径情景,其中四个独立的光信号同时通过芯片网格路由而不发生干扰。我们建立了四条独立的轨迹:端口2到15,7到27,10到24,以及32到19。对于这些路径,测量得到的归一化输出功率分别为0.892、0.91、0.88和0.954。这些高传输值表明,网格可以支持多个相交的信号流,动态地在边界上任意点之间创建光学连接。

最后,我们通过将网格配置为1×8光分配器,演示了它在广播应用中的能力。如图4c中的示意图所示,一个输入信号通过级联树结构分配到八个不同的输出端口(o21–o28)。光谱响应测量显示,在1560–1570 nm的波长范围内,所有八个通道的功率分布非常均匀。重叠的迹线表明平衡的分配比和宽带操作,证明该网格适用于一对多的信号分配任务。

3. 讨论

我们首次展示了一个扩展的可编程光子处理器,能够实现非挥发性操作,解决了目前限制可编程集成光子学扩展的功率瓶颈。通过将铁电BTO执行器集成到硅光子学六边形波导网格中,我们实现了一个平台,结合了非挥发性存储的零静态功率优势与动态信号处理所需的高速性能。尽管近期在缩小规模的演示中已经探索了非挥发性功能,例如使用相变材料(PCMs),但我们的工作代表了基于铁电执行器的完全可重构、通用六边形FPPGA的首次实现。

本工作的核心成就是将电路复杂性与能耗解耦。在传统的基于热光学相位移器的可编程电路中,维持特定电路配置需要持续的电偏置。每个执行器的典型功耗为1–10 mW,在包含数千个单元的规模化网格中,功耗可达到数十瓦,需要复杂的热管理方案来防止串扰和不稳定性。相比之下,我们基于BTO的架构在挥发模式下消耗非常低的功率(每个执行器560 nW/π)。此外,如果它以非挥发性模式驱动,一旦编程,状态便由铁电域定向保持,无需外部偏置。这种“设置并忘记”的能力表明,未来的处理器可以扩展到数千个执行器,而不需要相应增加静态功耗预算。

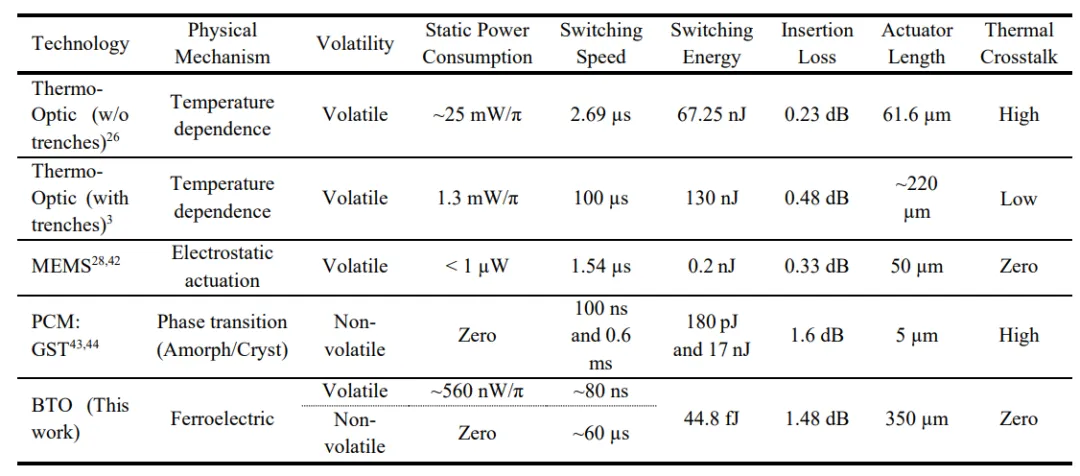

为了更好地理解铁电Si-BTO平台的性能,表1将我们的设备与当前用于可编程光子学的领先相位移技术进行了对比。

表1. 大规模光子电路的相位移机制性能基准

如表1所示,我们的设备弥补了现有开关技术之间的性能差距。相变材料通常依赖于无定形态和晶态之间的过渡,这可能引入显著的光吸收(每个元件>0.33 dB),并且受到较慢的晶化速度(毫秒级)的限制。相比之下,我们的BTO平台利用泊克尔斯效应,能够实现80纳秒的开关速度,比相变材料和热光学加热器快几个数量级。

然而,在光损耗方面,我们当前的原型每个PUC的插入损耗为1.48 dB。尽管这目前高于优化过的相变材料或MEMS设备的固有损耗,但必须区分这种衰减的来源。与相变材料不同,后者的损耗通常是材料状态的内在特性,我们设备中的损耗主要是由于混合集成过程中的模式过渡(收缩)所引起的,特别是在硅和Si-BTO波导之间。由于BTO本身在通信波长下是透明的,因此通过优化收缩几何形状和缓冲层厚度,未来几代设备有明确的工程路径可以将这些损耗减少到<0.5 dB。

尽管当前存在插入损耗,实验演示从可调FIR/IIR滤波器到矩形单位架构,验证了平台的光学鲁棒性。然而,重要的是要澄清在这些系统级实验中使用的操作模式。虽然单个单元已证明支持非挥发性存储,但这里呈现的复杂网格配置是在挥发性驱动模式下表征的。要在非挥发性模式下控制整个网格,需要一个能够独立分配特定编程脉冲到所有电极的电子接口。在我们当前的实验设置中,由于依赖单一脉冲源,因此这种寻址仅限于手动操作。因此,开发一个集成的电子开关矩阵来自动化脉冲分配,是完全释放平台在大规模电路中零静态功率潜力的关键下一步。

最后,与传统平台相比,依赖于泊克尔斯效应从根本上改善了热管理策略。与通过局部加热波导并固有地遭受相邻组件之间的热串扰的热光学相位移器不同,我们的铁电执行器是电场驱动的,不产生废热。这有效地消除了设备内部的热串扰,这是密集光子集成中的主要瓶颈。然而,铁电材料仍然对全球环境温度波动敏感(请参见补充说明4,了解设备温度依赖性的表征)。因此,尽管该系统没有自生热不稳定性,但仍需要使用热电冷却器(TEC)精确稳定芯片基板,以维持性能,防止外部环境变化的影响。

总之,非挥发性场可编程波导网格的实现从根本上改变了集成光子学的扩展前景。通过消除热光学方法中固有的静态功耗和热串扰,该平台克服了阻碍大规模光学处理器发展的主要瓶颈。尽管未来的努力必须解决插入损耗和电子共同集成问题,但本文展示的结果为可持续、高速光子计算提供了清晰的蓝图。这项技术将在下一代硬件中发挥至关重要的作用,能源效率和适应性将成为核心要素。

4. 方法

4.1 制造

用于BTO集成过程的200 mm基础晶圆是在CEA-Leti制造的,采用220 nm的硅-绝缘体-硅(SOI)平台,具有3 µm的埋氧化物(BOX)层。为了准备适合BTO粘接的表面,我们的目标是将氧化物的厚度控制在350 nm,通过连续的氧化物沉积和化学机械抛光(CMP)步骤来实现。最终测量结果确认,所得到的厚度约为365 nm(补充说明5)。随后,晶圆被转移到Lumiphase,进行BTO层的转移。对于硅被动器件和BTO相位移器之间的层间耦合,设计了硅波导的收缩结构,将模式传递到Si-BTO波导中。最后,通过光波导包层和通过通孔的金属化完成制造过程。

4.2 表征与测量

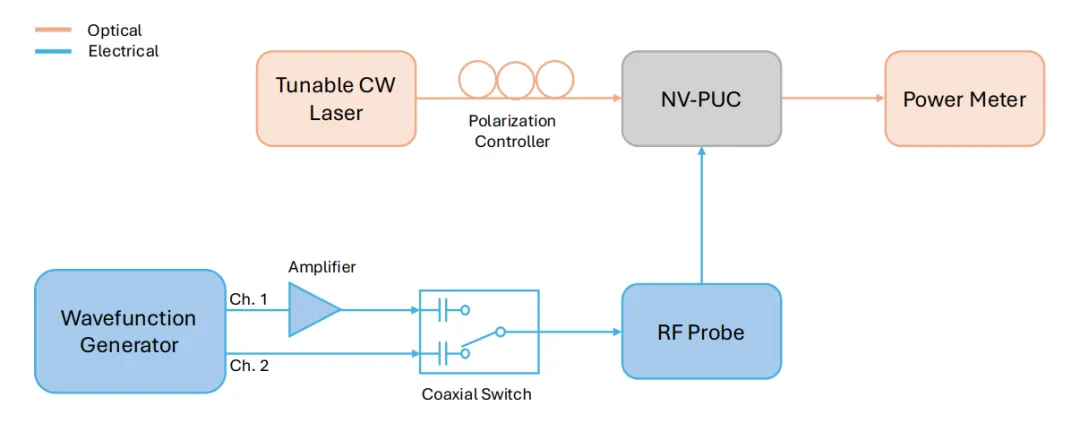

NV-PUC的表征是通过位于与六边形网格相同芯片上的测试结构进行的。初始实验设置包括一个可调的连续波(CW)激光器(EXFO T100S-HP),后接偏振控制器。光通过两个固定在8度倾斜楔形体上的光纤耦合器进入和离开PUC的光栅耦合器,这些光纤固定在锥形V型槽光纤夹具上。在PUC的输出端,使用可编程功率计(EXFO FTBx-1750)测量检测到的光功率。为了控制PUC执行器,使用250 µm间距的射频探针从波形发生器(Teledyne T3AFG120)中应用两种不同类型的信号。这些信号用于设置和擦除PUC的各种状态。

设置一个状态的程序从擦除铁电域状态开始。为此,施加一个1.3 MHz的正弦信号,幅度调制为下降波形(33.33 Hz),持续2秒,以重新组织铁电域为任意分布。随后,通过施加104个脉冲的序列来定义两个特定的铁电域状态(0和1),每个脉冲的持续时间为300 ns,电压为5 V或-5 V(根据状态0或1)。这种脉冲组合会导致两个方向的轮询状态达到饱和。设置初始状态(0或1)后,应用一个N脉冲(300 ns持续时间)的脉冲序列,具有特定的上限和下限幅度(VHL和VLL)。一旦设置了状态,电压源被关闭,并测量光输出功率(补充说明1)。擦除信号和设置状态的脉冲序列是使用相同的波形发生器生成的,每个设备通道一个。电放大器被放置在擦除信号的输出端,其输出与第二个通道(包含脉冲序列)连接到一个同轴开关(Radiall R570412000LP),用于顺序施加这两个信号。

对于网格测量,首先对设备进行了自动表征。为此,使用一组功率计(EXFO LTB-12 & FTBx-1750)监控所有网格输出端口的光功率。这一自动表征过程依赖于一个图形表示,该图形复制了网格的拓扑结构。我们选择一个固定的输入端口,并使用图形确定到其余端口的最短路径。通过优化每条路径的输出功率,我们依次表征沿该路径的各个MZI,并为所有其他端口重复该过程(补充说明2)。最后,使用被动组件测试仪(EXFO CT440)获取1560 nm周围的传输光谱,光谱分辨率为1 pm。

补充说明 1. 非挥发性操作的电驱动方案

光学表征设置

非挥发性可编程单元(NV-PUC)的表征是使用与六边形网格在同一芯片上制造的专用测试结构进行的。光学测量设置使用了可调的连续波(CW)激光器(EXFO T100S-HP)作为光源。为了确保最佳的耦合效率,输入光的偏振在耦合之前通过手动偏振控制器进行调整。

光通过PUC的光栅耦合器进入和离开是通过将两个切割好的光纤安装在8º倾斜的楔形体上,并使用锥形V型槽光纤夹具进行耦合实现的。通过设备传输的光功率通过可编程功率计(EXFO FTBx-1750)进行检测和分析。

电气控制

PUC的电气驱动是通过具有250 µm间距的射频(RF)探针进行的。这些探针提供由双通道任意波形发生器(Teledyne T3AFG120)生成的控制信号。信号路由被设计为能够在不需要人工干预的情况下顺序切换“擦除”信号和“写入/设置”信号:

通道 1(擦除线):连接到电放大器,以实现所需的电压合规性,从而重新组织域。

通道 2(脉冲序列/写入线):直接连接到输出开关。

这两个通道被路由到一个同轴开关(Radiall R570412000LP),允许精确地顺序将擦除和设置波形应用到PUC上。图S1显示了完整设置的示意图。

图S1. NV-PUC表征设置的示意图光学路径包括一个可调的连续波(CW)激光器、一个偏振控制器和一个功率计。电气驱动由双通道波形发生器管理;通道1(擦除)经过放大,而通道2(写入)则直接连接。一个同轴开关将适当的信号路由到射频探针,用于域擦除或状态设置。

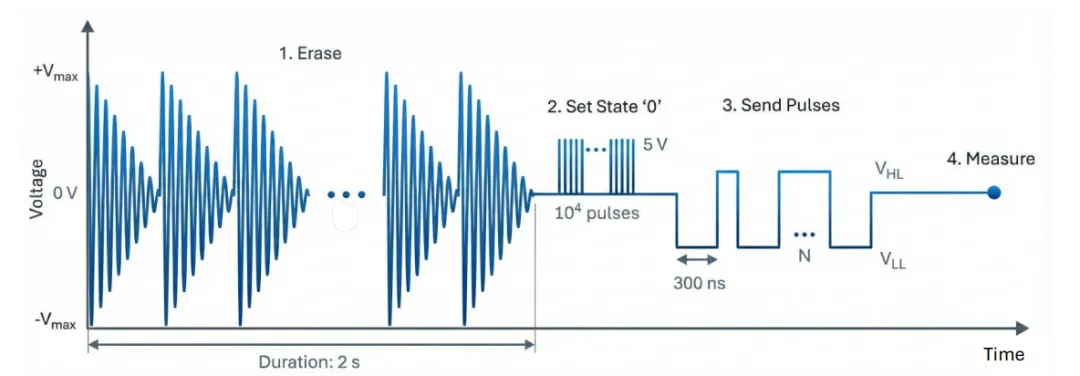

实验程序

为了准确表征铁电开关动态,定义了一个四步协议:步骤 I:域擦除(重置)。 为了消除先前测量中的滞后效应和历史效应,首先擦除铁电域状态。应用频率为1.3 MHz的正弦波,持续时间为2秒。该信号使用下坡波形(33.33 Hz)进行幅度调制,以逐渐减小电场强度,将域重新组织成任意的、随机分布的状态。

步骤 II:饱和(极化)。 随后,通过应用104个脉冲的序列,定义了两个特定的铁电域状态(状态0和状态1)。

脉冲持续时间:300 ns。

振幅:状态0为+5 V,状态1为-5 V。此脉冲组合使两个极化方向都达到饱和状态。

步骤 III:设置状态。 在设置初始饱和状态(0或1)之后,应用一组N个脉冲,每个脉冲的持续时间为300 ns(脉冲间隔同样为300 ns)。这些脉冲在特定的高电平(VHL)和低电平(VLL)振幅之间交替,以诱导部分开关。

步骤 IV:测量。 紧接着脉冲序列后,关闭电压源。然后,测量光学传输,以量化PUC状态中的非挥发性变化。

整个四个阶段中施加的电压信号的时间演化如图S2所示。

图S2. 电气驱动和测量协议表征序列包括四个步骤:

擦除:应用一个正弦信号(1.3 MHz),并用下坡波形(33.33 Hz)幅度调制,持续2秒,以随机化铁电域并消除历史效应。

初始化:通过施加104个脉冲(5 V),将设备极化到饱和状态(状态‘0’)。

驱动:施加一组N个脉冲(30 ns持续时间,300 ns间隔),具有交替的高低幅度,以诱导部分开关。

测量:将电压设置为0 V(零偏置),以测量非挥发性的光学传输。

补充说明 2. 网格的设置与基于图形的自动化表征

实验设置

对于网格测量,设备使用自定义构建的设置进行了自动化表征。使用一组功率计(EXFO LTB-12主机与FTBx-1750模块)来监控网格输出端口的光功率。主动组件通过多通道电压源(Qontrol Ltd.)驱动。

自动控制算法

该表征例程依赖于网格拓扑的有向图抽象 ( G(V, E) ),其中节点代表Mach-Zehnder干涉仪(MZI)端口,边代表波导链接2。表征过程包括三个主要步骤(见算法1):

路径寻找: 对于给定的光学端口(源端口、目标端口)对,算法使用Dijkstra算法计算最短路径。施加几何约束以避免物理弯曲超过最大角度(( \theta_{\text{max}} = 120^\circ )),确保不会通过同一个MZI返回(尽管也可以使用其他方法,如有向图)。

路径优化: 一旦路径定义完成,沿路径的MZI的电压会同时通过粒子群优化(PSO)进行优化,以最大化目标端口的光功率。

串扰抑制: 为了最小化串扰,算法识别“相邻”MZI(共享耦合器与活动路径相关但不属于活动路径的节点)。主路径会暂时失调以诱导泄漏,随后通过PSO优化相邻MZI,以最小化输出端口检测到的功率,从而有效地阻塞备用路径。

单个组件表征: 在路由配置完全建立后,系统执行组件的顺序扫描。沿路径的每个MZI会在电压范围0-12 V内单独扫描,同时保持路径的其他部分和相邻的MZI在优化状态下。生成的传输曲线会存储在数据集中,并且特定MZI会返回其最优电压,然后再进行下一个组件的扫描。

不平衡Mach-Zehnder干涉仪(FIR滤波器)

同样,正文中介绍了路径差为 ( \Delta L = 2L_{PUC} ) 和 ( 4L_{PUC} ) 的有限脉冲响应(FIR)滤波器。这里,我们将这些测量扩展到一个高阶延迟线配置,路径差为 ( \Delta L = 8L_{PUC} )(图S5)。该配置(UMZI 3)生成了...

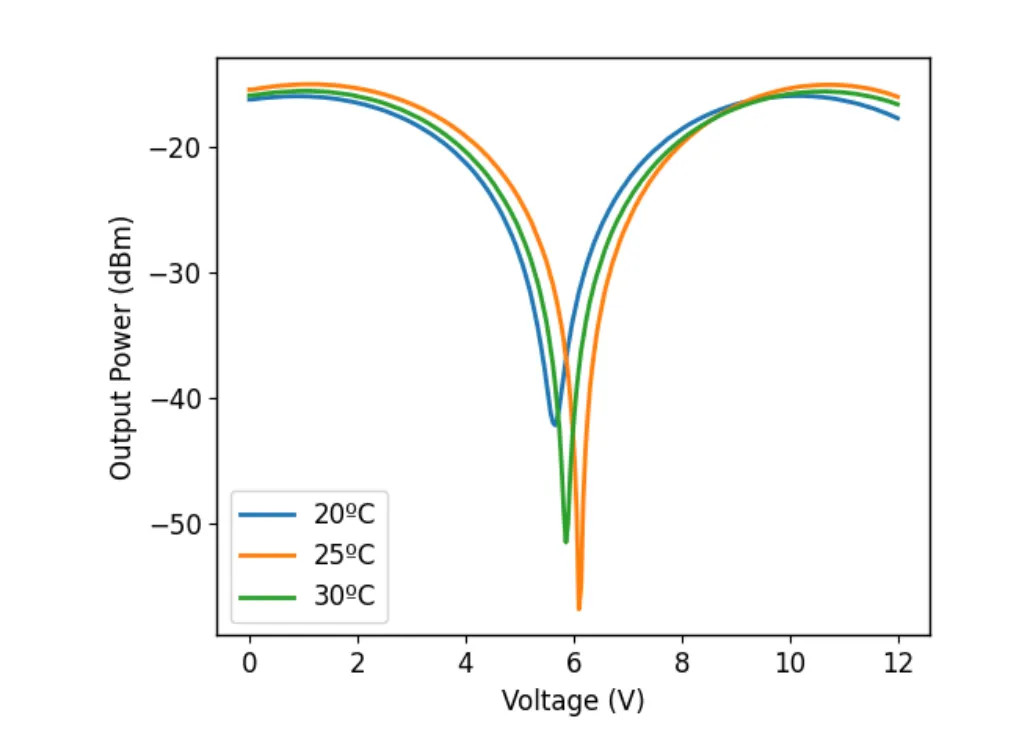

补充说明 4. 钛酸钡相位移器的热敏感性

为了确保电光重构的稳定性,我们表征了钛酸钡(BTO)相位移器的热敏感性。我们在不同热条件下,使用热电冷却器(TEC)精确控制芯片温度,对网格中的一个代表性MZI进行了隔离并表征。我们在三个不同温度设定点下,进行0到12 V的电压扫描:20ºC、25ºC和30ºC。如图S6所示,工作温度的变化会引起相位响应的偏移,改变实现破坏性干涉所需的偏置电压。在25ºC与20ºC之间的电压偏差为0.45 V,在25ºC与30ºC之间的电压偏差为0.24 V。因此,在表征和测量过程中,保持相同的温度是必要的。特别地,在25ºC时的测量(橙色曲线)展示了最深的共振陷波,达到了42 dB的抑制。相反,偏离25ºC到30ºC时,导致了ER的退化和光谱的偏移。因此,所有本研究中的实验都在通过TEC保持的恒定温度25ºC下进行。

图S6. 带有BTO相位移器的MZI的热依赖性

补充说明 5. 制作的硅波导

光子电路是在200 mm基础晶圆上加工的,晶圆由CEA-Leti制造,使用了具有3 µm厚埋氧化物(BOX)层的硅-绝缘体-硅(SOI)平台。虽然平台名义上基于220 nm的硅层,但实际制造的结构经过了表征验证。

为了准备适合BTO异质集成的表面,要求进行平面化的顶部包层。目标的顶部氧化物厚度为350 nm,这是通过一系列氧化物沉积步骤和随后的化学机械抛光(CMP)平面化步骤实现的。

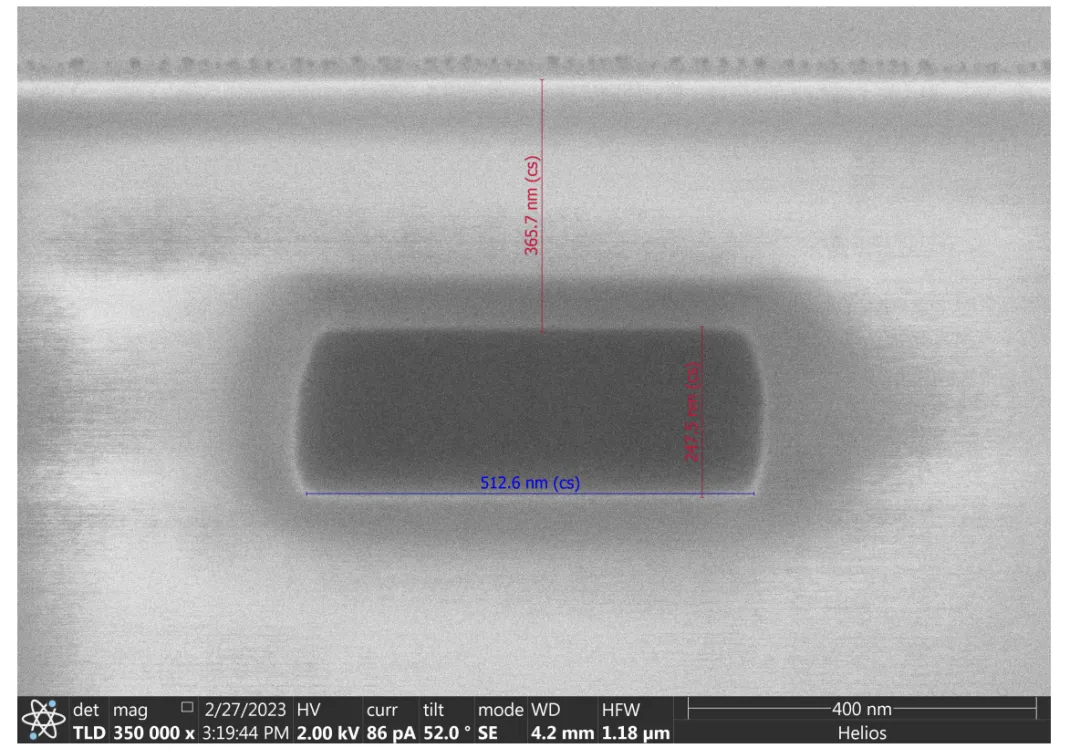

图S7. 制作的硅波导的横截面SEM分析

最终验证是通过扫描电子显微镜(SEM)对横截面进行的(图S7)。成像确认了坚固的矩形波导轮廓,核心宽度约为512.6 nm,高度为242.5 nm。此外,关键的顶部氧化物厚度测量为365.7 nm。该值略超出名义目标,但确保了足够的平面化余量,以便后续直接晶圆粘接BTO薄膜。