Linux 驱动开发基础详解(3):pinctrl 子系统

- 2026-03-26 09:17:38

Linux 驱动开发基础详解(3):pinctrl 子系统

“前情回顾:在上一节的学习中,我们编写了基于设备树的 LED 驱动。但大家可能会发现,我们依然像裸机开发那样,通过直接获取并操作 GPIO 相关的底层寄存器来实现驱动。

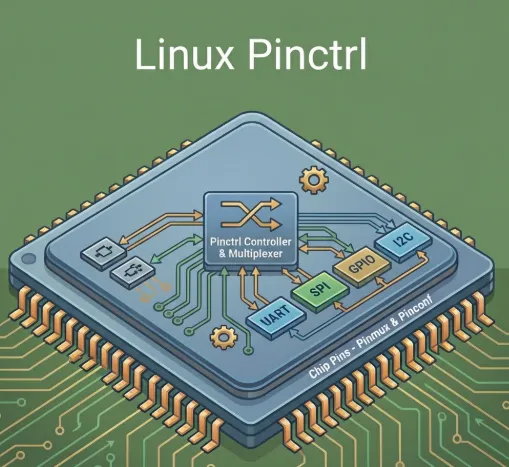

然而,Linux 是一个庞大而高度抽象的系统,这种“原始”的寄存器硬编码方式不仅繁琐,而且违背了 Linux 驱动 “分离与分层” 的设计思想。为此,Linux 内核引入了

pinctrl和gpio子系统。本篇将聚焦于:**pinctrl子系统**。

01 学习重点

在掌握了设备树基本语法后,本节我们需要搞清以下两个核心问题:

为什么需要 pinctrl 子系统?它到底负责干什么? 如何在设备树(Device Tree)中正确使用和配置 pinctrl?

02 告别裸机,引入 pinctrl?

传统的“裸机式”配置方式

回顾上一节 LED-GPIO 的初始化过程,我们通常需要做三件事:

查地址:在设备树节点中设置 reg属性,填入相关的寄存器物理地址。配引脚(PIN):初始化复用(MUX)寄存器和电气属性(PAD)寄存器,设置引脚的复用功能(如设为 GPIO)、上下拉、速度等。 配 GPIO:初始化 GPIO 控制寄存器,设置输入/输出方向及电高等。

对于绝大多数 32 位 SOC 而言,引脚支持多路复用(Multiplexing)。如果每个驱动都自己去查手册、算地址、配寄存器,代码将极度冗余且难以维护。

pinctrl 子系统的使命

为了将开发者从繁琐的寄存器配置中解放出来,Linux 推出了 pinctrl 子系统。它的核心工作内容只有三个:

获取 PIN 信息:从设备树中读取引脚配置。 设置复用功能(MUX):根据信息,将引脚配置为特定的功能(如 I2C、SPI、GPIO)。 设置电气特性(PAD):配置引脚的上/下拉、驱动能力、速度等。

💡 优势:引入 pinctrl 后,驱动开发者只需要在设备树中按规则写好 PIN 的属性,底层的寄存器读写全由内核 pinctrl 驱动自动配置!

03 实战:在设备树中配置 pinctrl

我们以 NXP 的 I.MX6ULL 芯片为例,实现在设备树(.dtsi 文件)中配置 pinctrl。

1. 找到 IOMUXC 节点

在 I.MX 系列芯片中,引脚由 IOMUXC 外设管理。在设备树中,我们需要找到对应的 iomuxc 节点:

iomuxc: iomuxc@020e0000 {

/* 内核会根据 compatible 匹配对应的 pinctrl 驱动文件 */

compatible = "fsl,imx6ul-iomuxc";

/* IOMUXC 外设的寄存器基地址为 0x020e0000,长度为 0x4000 */

reg = <0x020e0000 0x4000>;

};

2. 追加 PIN 配置信息

我们需要配置 UART1_RTS_B 这个引脚,将其复用为 GPIO1_IO19。我们需要在 iomuxc 节点下添加特定的子节点:

&iomuxc {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_hog_1>;

imx6ul-evk {

/* 自定义的节点名称,常以驱动名或功能命名 */

pinctrl_hog_1: hoggrp-1 {

/* fsl,pins 是核心属性,里面存放具体的引脚配置 */

fsl,pins = <

/* 格式:<宏定义(复用配置) 自定义数值(电气特性配置)> */

MX6UL_PAD_UART1_RTS_B__GPIO1_IO19 0x17059

MX6UL_PAD_GPIO1_IO05__USDHC1_VSELECT 0x17059

MX6UL_PAD_GPIO1_IO09__GPIO1_IO09 0x17059

MX6UL_PAD_GPIO1_IO00__ANATOP_OTG1_ID 0x13058

>;

};

};

};

⚠️ 注意解析: 在 fsl,pins 属性中,每一行代表一个引脚的配置,由两部分组成:

前半部分(宏): MX6UL_PAD_UART1_RTS_B__GPIO1_IO19,决定引脚的复用功能。后半部分(数值): 0x17059,决定引脚的电气特性(由用户查手册自行计算填写,用于配置上/下拉、驱动能力等)。

04 深度解析:宏定义

像 MX6UL_PAD_UART1_RTS_B__GPIO1_IO19 这么长的宏,到底代表了什么呢? 设备树是支持 C 语言 #include 语法的,这个宏定义在内核的 .h 头文件中(如 imx6ul-pinfunc.h)。

宏定义源码

在头文件,关于 UART1_RTS_B 的复用宏多达 8 个(代表它可以复用为 8 种不同的功能):

/* 格式: <mux_reg conf_reg input_reg mux_mode input_val> */

#define MX6UL_PAD_UART1_RTS_B__UART1_DCE_RTS 0x0090 0x031C 0x0620 0x0 0x3

#define MX6UL_PAD_UART1_RTS_B__UART1_DTE_CTS 0x0090 0x031C 0x0000 0x0 0x0

#define MX6UL_PAD_UART1_RTS_B__ENET1_TX_ER 0x0090 0x031C 0x0000 0x1 0x0

#define MX6UL_PAD_UART1_RTS_B__USDHC1_CD_B 0x0090 0x031C 0x0668 0x2 0x1

#define MX6UL_PAD_UART1_RTS_B__CSI_DATA05 0x0090 0x031C 0x04CC 0x3 0x1

#define MX6UL_PAD_UART1_RTS_B__ENET2_1588_EVENT1_OUT 0x0090 0x031C 0x0000 0x4 0x0

/* ⚠️这是我们用到的宏,将其复用为 GPIO1_IO19 ⚠️ */

#define MX6UL_PAD_UART1_RTS_B__GPIO1_IO19 0x0090 0x031C 0x0000 0x5 0x0

#define MX6UL_PAD_UART1_RTS_B__USDHC2_CD_B 0x0090 0x031C 0x0674 0x8 0x2

5个十六进制数

宏定义后面跟着的 0x0090 0x031C 0x0000 0x5 0x0 这 5 个数字,正是内核 pinctrl 驱动用来操作底层寄存器的方式。

它们对应 <mux_reg conf_reg input_reg mux_mode input_val>,具体含义如下表:

0x020e0000) | |||

|---|---|---|---|

| mux_reg | 0x0090 | 复用寄存器偏移地址 | 0x020e0000 + 0x0090 = 0x020e0090(指向 MUX_CTL 寄存器) |

| conf_reg | 0x031C | 电气特性寄存器偏移地址 | 0x020e0000 + 0x031C = 0x020e031C(指向 PAD_CTL 寄存器) |

| input_reg | 0x0000 | 输入寄存器偏移地址 | |

| mux_mode | 0x5 | 复用寄存器(mux_reg)要写入的值 | 0x020e0090 的值配置为 0x5,即可复用为 GPIO。 |

| input_val | 0x0 | 输入寄存器要写入的值 |

配置完成

现在,结合我们在设备树中写的那行代码:MX6UL_PAD_UART1_RTS_B__GPIO1_IO19 0x17059

相当于我们向 pinctrl 子系统下达了如下指令:

““把偏移地址为

0x0090的寄存器值写为0x5(搞定复用);然后把偏移地址为0x031C的寄存器值写为0x17059(搞定电气特性)。”

底层的 fsl,imx6ul-pinctrl 驱动拿到这些参数后,会自动完成所有寄存器的映射和写入,完全不需要我们在驱动 C 代码中写一行 ioremap 映射!

05 小结

通过本节学习,我们掌握了 pinctrl 子系统的工作原理。后续驱动开发中,配置引脚的标准姿势为:

| 1 | .h),找到目标引脚的复用宏定义。 | |

| 2 | 0x17059)。 | |

| 3 | .dts)的 iomuxc 节点下新建子节点,在 fsl,pins 中填入 <宏定义 电气特性值>。 | |

| 4 |

搞定了引脚的复用和上下拉(pinctrl),这只是第一步。下一节,我们将学习如何使用 GPIO 子系统 来真正控制这个被配置好的引脚(输出高低电平或读取输入状态)。